A software profiling tool records the address held in the Program Counter (PC) every 1 ms. The software function that resides at each recorded address can be determined by the profiling tool. The percentage of time spent in each function is calculated from the percentage of recorded addresses where each function is resident.

Which one of the following statements is FALSE?

Which of the following statements regarding Strongly-ordered memory is architecturally FALSE?

Which of the following is a REQUIRED feature in the ARMv7 architecture?

Which one of the following debug methods is the least intrusive for analyzing a timing related bug?

In an ARMv7-A processor, which control register is used to enable the Memory Management Unit (MMU)?

The instruction LDR pc, [ r1 ] takes longer to execute on a particular system, than the instruction LDR r0, [ r1 ]. In both cases, r1 points to the same address in external memory.

Which of the following is the most likely explanation of why it takes more cycles?

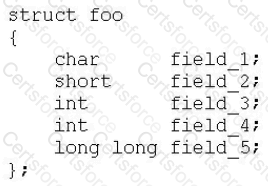

According to the EABI. what would the C size of () operator return when given the following structure?

The disassembly of a program written in C shows calls to the function__aeabi_fadd. Which one of these compiler floating point options could have been used?

The effect of clicking the Stop button in a debugger is to:

An interrupt handler contains the following instruction sequence at the end. The purpose of these instructions is to clear the interrupt request in the interrupt controller and then safely re-enable interrupts.

STR r0, [r1] ; write to interrupt controller register to clear interrupt request

CPSIE i ; re-enable IRQ interrupts

Which of the following instructions should be placed at position